معماری پردازنده Telum II

آیبیام در جریان برگزاری کنفرانس Hot Chips 2024، به تشریح جزییات بیشتری در ارتباط با معماری پردازنده آینده خود به نام معماری پردازنده Telum II و شتابدهنده IBM Spyre پرداخت. این فناوریهای جدید با هدف افزایش چشمگیر ظرفیت پردازش در مینفریمهای نسل بعدی IBM Z طراحی شدهاند. این افزایش ظرفیت پردازش، شتابدهی به هر دو نوع، مدلهای سنتی هوش مصنوعی و مدلهای زبانی بزرگ را از طریق به کارگیری روش جدید یادگیری گروهی (Ensemble) در دنیای هوش مصنوعی، امکانپذیر میکنند. با انتقال طیف گستردهای از پروژههای هوش مصنوعی مولد که از مدلهای زبانی بزرگ (LLM) استفاده میکنند از مرحله اثبات مفهومی به تولید، تقاضای شرکتها برای راهحلهای کم مصرف، ایمن و مقیاسپذیر به اولویت اصلی بسیاری از شرکتهای پیشرو تبدیل شده است.

مورگان استنلی پژوهشی در ارتباط با میزان تقاضای انرژی برای هوش مصنوعی مولد انجام داده و پیشبینی رشد سالانه 75% را انتظار دارد. پیشبینیها نشان میدهند که مصرف انرژی هوش مصنوعی تا سال 2026 میتواند با مصرف انرژی در کشوری مثل اسپانیا، برابری کند. این موضوع مشتریان آیبیام را بر آن داشته است به سراغ مدلهای زیرساختی که اندازه مناسبی دارند به همراه رویکردهای ترکیبی برای بارهای کاری هوش مصنوعی استفاده کنند.

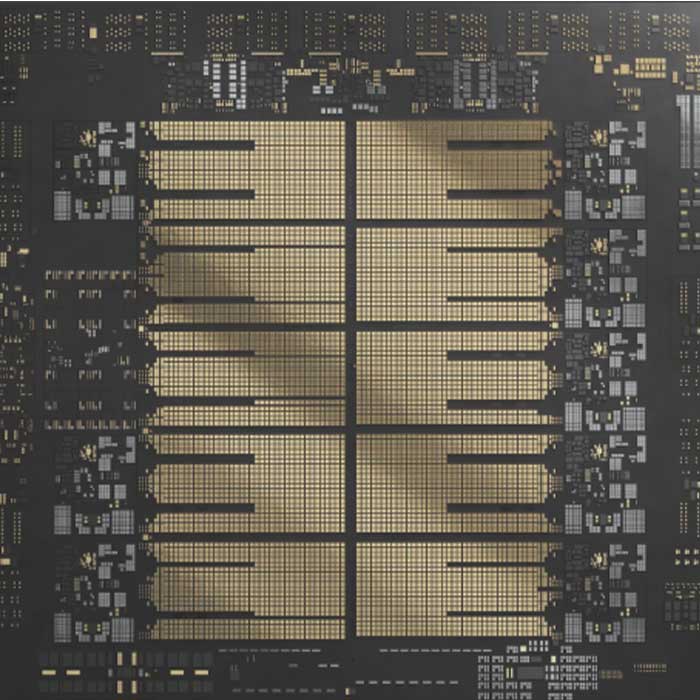

معماری پردازنده Telum II برای تامین توان محاسباتی نسل بعدی سیستمهای IBM Z طراحی شده است. آیبیام در طراحی جدید، فرکانس پردازنده را افزایش داده، پشتیبانی از ظرفیت بالای حافظه را بهبود بخشیده، 40% حافظه کش را بیشتر کرده و یک هسته شتابدهنده هوش مصنوعی یکپارچه را تعبیه کرده است. پردازنده جدید یک واحد پردازش داده (DPU) متصل به هم را معرفی میکند که برای شتابدهی به پروتکلهای پیچیده IO، شبکهسازی و ذخیرهسازی در سیستم اصلی طراحی شده است. DPU عملیات سیستم را سادهتر میکند و عملکرد مولفههای اصلی را بهبود میبخشد. همین مسئله باعث شده تا پردازنده Telum II برای راهحلهای محاسباتی سازمانی و پشتیبانی از LLM و تراکنشهای پیچیده صنعتی مناسب باشد.

مکمل پردازنده Telum II، شتابدهنده IBM Spyre است که قابلیتهای محاسباتی اضافی در ارتباط با هوش مصنوعی را ارائه میدهد. تراشههای Telum II و Spyre دسترسی به یک معماری مقیاسپذیر را امکانپذیر میکنند که از روشهای گروهی مدلسازی هوش مصنوعی پشتیبانی میکند و قادر به پشتیبانی از ترکیب چند مدل یادگیری ماشین یا یادگیری عمیق هوش مصنوعی با LLMهای رمزگذار هستند. این راهحل از نقاط قوت هر معماری برای ارائه نتایج دقیقتر و قویتر نسبت به مدلهای انفرادی استفاده میکند. شتابدهنده IBM Spyre، که به عنوان یک پیشنمایش در Hot Chips 2024 معرفی شد، به عنوان یک قطعه اختیاری در آینده نزدیک در دسترس قرار خواهد گرفت. این شتابدهنده از طریق یک آداپتور 75 وات PCIe به سیستم متصل میشود و بالاترین سطح از مقیاسپذیری را در اختیار شرکتها قرار میدهد.

تینا تارکینو، معاون مدیریت محصول IBM Z و LinuxONE، بر تعهد آیبیام برای تضمین دسترسی به جدیدترین فناوریها برای مشتریان خبر داده و اعلام داشته است که آیبیام تقاضای رو به افزایش هوش مصنوعی کاملا زیرنظر دارد و محصولات خود را مطابق با درخواستهای مشتریان آماده خواهد کرد. او اظهار داشت که پردازنده Telum II و شتابدهنده Spyre برای ارائه راهحلهای محاسباتی سازمانی با عملکرد بالا، ایمن و کم مصرف طراحی شدهاند. این نوآوریها، که سالها در حال توسعه بودهاند، در نسل بعدی پلتفرم IBM Z معرفی خواهند شد و به مشتریان امکان میدهند تا از LLM و هوش مصنوعی مولد در مقیاس کلان بهرهبرداری کنند.

پردازنده Telum II و شتابدهنده IBM Spyre توسط سامسونگ فاندری، شریک دیرینه آیبیام، با استفاده از لیتوگرافی 5 نانومتری بر مبنای عملکرد بالا و مصرف کم تولید خواهند شد. این فناوریها با هم از طیف وسیعی از کاربردهای پیشرفته مبتنی بر هوش مصنوعی پشتیبانی خواهند کرد که مزیتهای رقابتی جدید در اختیار شرکتها قرار خواهند داد. به عنوان مثال، این ترکیب را میتوان به منظور بهبود عملکرد مدلهایی که در زمینه تشخیص تقلب در امور مالی مورد استفاده قرار میگیرند به کار گرفت تا از طریق ترکیب مدلهای هوش مصنوعی Ensemble با شبکههای عصبی سنتی، روند انجام عملیات به شکل دقیقتری انجام داد.

پردازنده Telum II قرار است با هشت هسته با عملکرد بالا با فرکانس 5.5 گیگاهرتز، 36 مگابایت حافظه کش L2 برای هر هسته و 40% افزایش ظرفیت حافظه کش روی تراشه، به مجموع 360 مگابایت، طراحی و عرضه شود. حافظه کش سطح 4 مجازی 2.88 گیگابایت برای هر دراور پردازنده (Processor drawer) در نظر گرفته شده است که 40% افزایش نسبت به نسل قبلی را نشان میدهد. شتابدهنده هوش مصنوعی یکپارچه اجازه میدهد تا فرآیند استنتاج هوش مصنوعی به شکل توکار با کمترین تاخیر و بالاترین عملکرد انجام شود که چهار برابر افزایش ظرفیت محاسباتی برای هر تراشه را نسبت به نسل قبلی ارائه میدهد. علاوه بر این، واحد شتابدهی ورودی/خروجی جدید DPU، که در تراشه Telum II یکپارچه شده است، برای بهبود رسیدگی به دادهها با 50% افزایش تراکم ورودی/خروجی طراحی شده است و کارایی کلی و مقیاسپذیری IBM Z را برای بارهای کاری کلان و برنامههای داده محور بهبود میبخشد.

لازم به توضیح است که شتابدهنده IBM Spyre، یک شتابدهنده رده سازمانی است که برای رسیدگی به نیازهای مدلهای پیچیده هوش مصنوعی و کاربردهای خاص منظوره هوش مصنوعی مولد طراحی شده است. این شتابدهنده توانایی پشتیبانی از 1 ترابایت حافظه را دارد که در هشت کارت در یک کشوی ورودی/خروجی منظم توزیع شدهاند و از بارهای کاری هوش مصنوعی در سیستم اصلی پشتیبانی میکنند، در حالی که مصرف برق آن از 75 وات برای هر کارت تجاوز نمیکند. هر تراشه دارای 32 هسته محاسباتی است که از انواع دادههای int4، int8، fp8 و fp16 پشتیبانی میکنند تا بتوانند به نیازهای برنامههای هوش مصنوعی با تاخیر کم و توان عملیاتی بالا پاسخ دهند.

پردازنده Telum II به عنوان نیروی محرکه پلتفرمهای نسل بعدی IBM Z و IBM LinuxONE عمل خواهد کرد و در سال 2025 در دسترس خواهد بود. شتابدهنده IBM Spyre، که در حال حاضر در وضعیت پیشنمایش فنی قرار دارد، نیز در سال 2025 در دسترس خواهد بود.