رونمایی Ampere از معماری AmpereOne

کنفرانس Hot Chips برای بسیاری از فعالان صنعت خبرهای خوشی را به همراه داشت و نشان داد که شرکتهای فعال در حوزه فناوری و به ویژه تولید پردازنده به شکل جدی در حال ساخت تراشههایی هستند که بتواند به نیازهای سنگین محاسباتی مراکز داده در ارتباط با هوش مصنوعی و آموزش مدلهای هوشمند پاسخ دهد. در این کنفرانس، شرکت Ampere جزییات بیشتری در ارتباط با معماری پردازندههای جدید خود منتشر کرد. در این مطلب قصد داریم، ویژگیهای کلیدی این معماری مثل موتور پیشبینی جدید، طراحی هسته و راهحل برچسبگذاری حافظه را مورد بررسی قرار دهیم.

نکات کلیدی معماری AmpereOne

از نکات برجسته و مهم کنفرانس امسال به موارد زیر باید اشاره کرد:

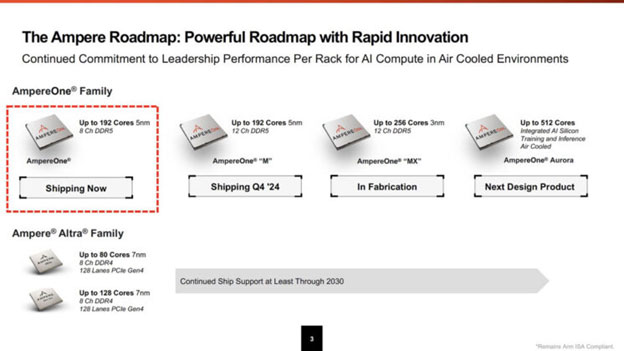

نقشه راه ApmereOne: شرکت Ampere، قصد دارد یک پردازنده 192 هستهای 5 نانومتری با 12 کانال DDR5 در سه ماهه آینده (انتهای سال 2024 میلادی) و سپس یک پردازنده 256 هستهای مبتنی بر لیتوگرافی 3 نانومتری را سال آینده (2025 میلادی) عرضه کند.

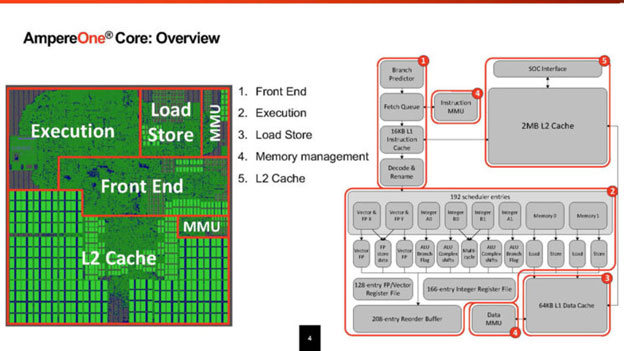

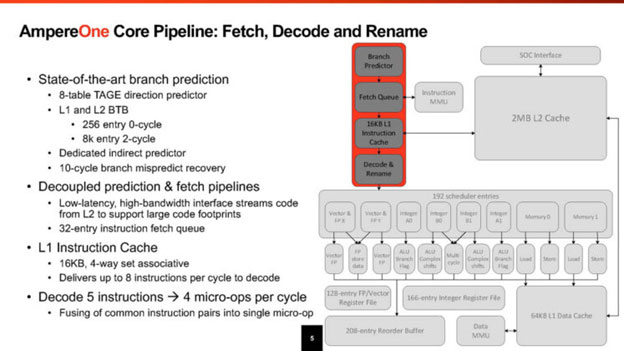

معماری هستههای تراشه AmpereOne را در شکل زیر مشاهده میکنید.

طراحی هسته: AmpereOne دارای یک موتور پیشبینی جدید است. این موتور استنتاجی قرار است به مشتریان ابری این شرکت که نیازمند تراشهای با عملکرد بالا هستند کمک کند محاسبات را در زمان کوتاهتری انجام دهند و همچنین بتوانند به ارزیابی دقیقتر عملکرد پردازنده در بارهای کاری مختلف بپردازند.

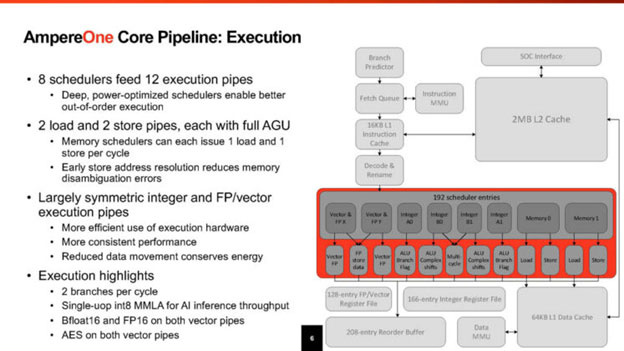

در معماری داخلی تراشه، هشت مدار زمانبندی وجود دارند که به دوازده خط انتقال، دستورالعملها را ارسال میکنند. این تراشه دارای خطوط اجرایی برای محاسبات اعشاری و برداری است، اما این خطوط بیشتر برای انجام محاسبات اعداد صحیح طراحی شدهاند که در محیطهای ابری رایج هستند.

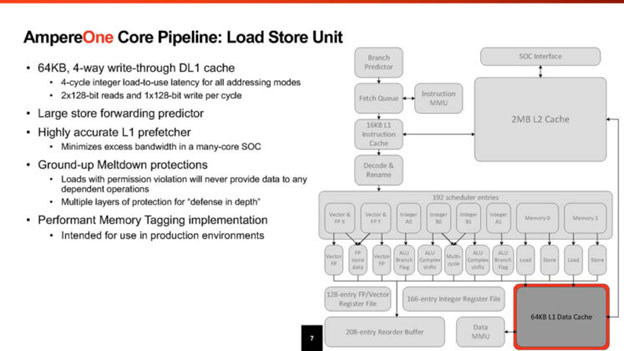

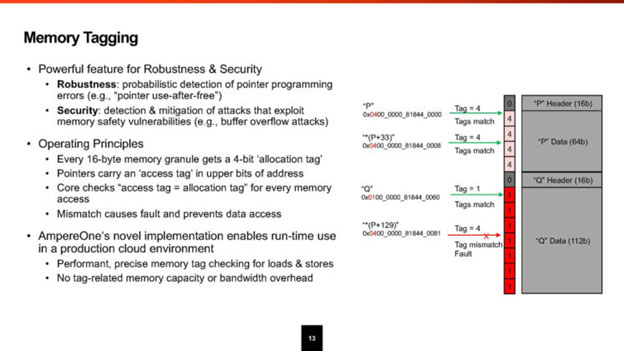

زیرسیستم حافظه: واحد بارگذاری ذخیرهسازی دارای یک راهحل برچسبگذاری حافظه است که میتواند در محیطهای تولیدی استفاده شود.

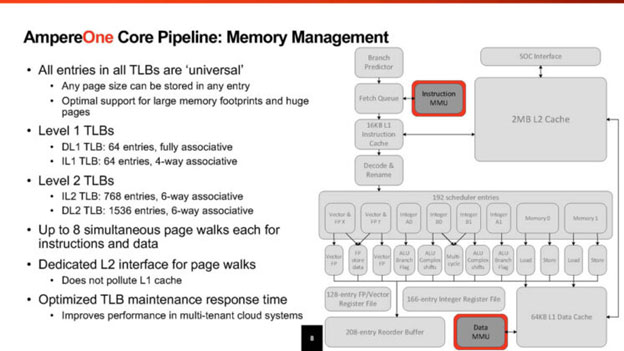

همه ورودیها در TLB یکسان هستند. لازم به توضیح است که در معماری آمپره، ما تنوع TLB را نداریم، بنابراین پیچیدگی کاهش پیدا کرده و روند ارسال و دریافت دستورالعملها نیز سریعتر میشود.

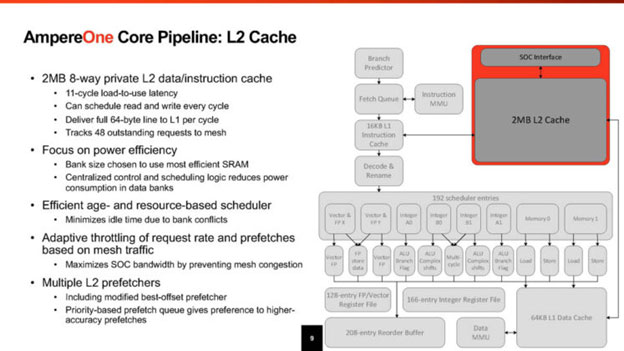

حافظه کش: آمپره وان به جای یک حافظه کش L3 بزرگ، از یک حافظه کش L2 بزرگتر 2 مگابایتی استفاده میکند. این حافظههای کش L2 اختصاصی هستند تا اطمینان حاصل شود روند انجام محاسبات به شکل دقیق مختص به بارهای کاری مشخص خواهد بود. این حافظه کش میتواند عملیات خواندن و نوشتن را برای هر چرخه زمانبندی کند. همچنین، حداکثر پهنای باند را برای مدار SOC ارائه میدهد.

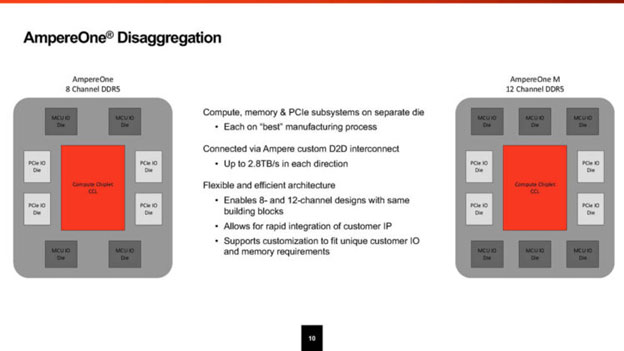

زیرسیستمهای روی تراشه: AmpereOne دارای زیرسیستمهای محاسباتی، حافظه و PCIe است. کنترلکنندههای PCIe و حافظه با فناوری 7 نانومتری TSMC ساخته شدهاند. این تراشهها با استفاده از یک اتصال بین تراشهای با سرعت 2.8 ترابایت بر ثانیه به هم متصل میشوند. آمپره میتواند با استفاده از همان پلتفرم، تا 12 کانال DDR5 را مقیاسبندی کند و همچنین آیپی کلاینت را ادغام کند.لازم به توضیح است که 8 و 12 کانال روی بلوکهای سازنده یکسانی فعال میشوند.

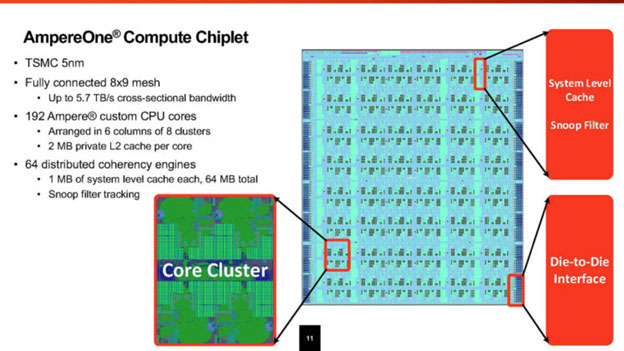

تراشه محاسباتی: تراشه محاسباتی اصلی AmpereOne با فناوری 5 نانومتری TSMC ساخته شده است. هر خوشه هسته، یک گروه از چهار هسته سفارشی آمپره را در اختیار دارد. همچنین، 64 موتور همگرا توزیع شده وجود دارد که هر کدام دارای 1 مگابایت حافظه کش L3 هستند. در مجموع، 64 مگابایت حافظه کش L3 وجود دارد که در شرق و غرب، اتصالات بین تراشهای قرار دارند.

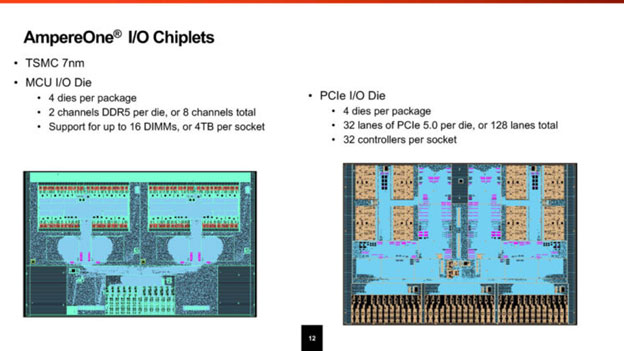

اتصال تراشهها: تراشه محاسباتی به تراشههای MCU (حافظه) و PCIe I/O متصل است. همچنین، تراشه حافظه دارای دو کانال DDR5 و PCIe I/O دارای 32 خط PCIe Gen5 است. این در حالی است که چهار تراشه PCIe روی بسته، 128 خط PCIe Gen5 را فراهم میکنند.

ویژگیهای اضافی: برچسبگذاری حافظه میتواند به یافتن خطاهای نرمافزاری و همچنین کاهش حملات سرریز بافر کمک میکند.

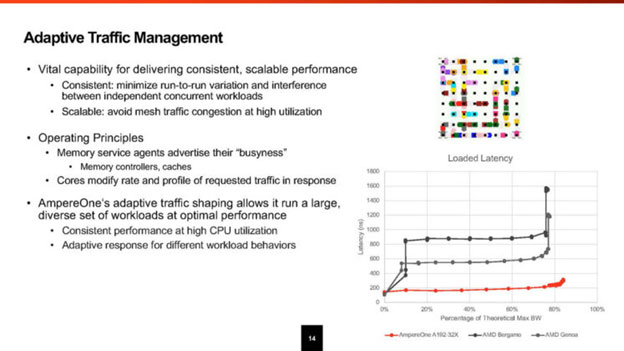

تراشه AmpereOne دارای مدیریت تطبیقی ترافیک تراشه است تا اثرات همسایگی و نویزهای بالا را در CPUهای ابری به حداقل برساند.

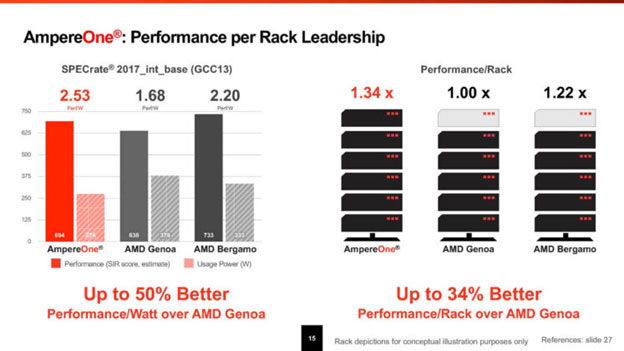

همانگونه که در شکل زیر مشاهده میکنید، این پردازنده برای محیطهای ابری با نیازهای خاص طراحی شده است.

کلام آخر

همانگونه که مشاهده میکنید، شرکتهای بزرگ تولیدکننده تراشههای اختصاصی، به یکباره تغییرات بزرگی در معماری سختافزار محصولات خود به وجود آوردهاند تا بتوانند به نیازهای روزافزون شرکتها و به ویژه ارائهدهندگان خدمات ابری پاسخ دهند. آمپره با معماری جدید خود نشان داده است، بازاری را به عنوان هدف انتخاب کرده است که مشتریان آن ارائهدهندگان خدمات ابری هستند که خود به طیف بسیار گستردهای از شرکتها و کاربران خدمترسانی میکنند.